- Blackberry KEYone(現地回線)

- iPhone SE(日本回線)

- EOS Digital 7D

- Cube PC(Core i7 7700)

- Surface Pro 4(Core i5 6300U)

- MacBook Air 13" 6-2(Early 2014, Core i5 4260U)

- GPD Pocket

- Lenovo TAB4 8 Plus 64GB

- Garmin Forerunner 225

- Huawei Watch 2 Classic

- Bose Quiet Comfort 35

(改訂版)DE0-CVでNios II

さらに新しいツールに慣れるため、IP統合の復習としてNios IIを組み込んだ簡単なモジュールを作る。

やっていることは

Qsysを使ってNios IIを組み込んだモジュールを作成する - 米国で働く技術系サラリーマンのボヤキ on はてブロ

と、

Quartus IIでQsysで作成したモジュールを組み込む - 米国で働く技術系サラリーマンのボヤキ on はてブロ

とほぼ同じことだ。

Quartus Primeでプロジェクトを作成

Platform Designer(旧Qsys)でNios IIを組み込んだモジュールを作成する

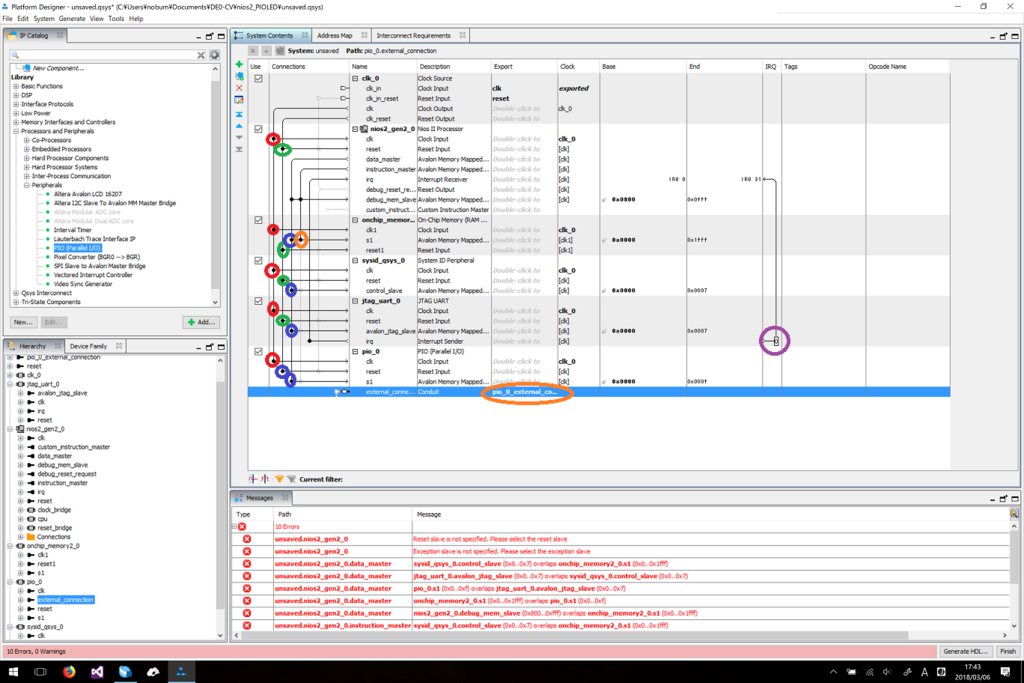

- "Tool" -> "Platform Designer"を起動、"IP Catalog"から以下のIPを組み込んでいく

- "Processors and Peripherals" -> "Embedded Processor" -> "Nios II Processor"を選択、"Main"タグで"Nios II Core"は"Nios II/e"を選択、他はデフォルトで"Finish"

- "Basic Function" -> "On Chip Memory" -> "On-Chip Memory (RAM or ROM)"を選択、"Size" -> "Total Memory Size"を"8192(bytes)"に変更、他はデフォルトで"Finish"

- "Basic Function" -> "Simulation: Debug and Verification" -> "Debug and Performance" -> "System ID Peripheral"を選択、デフォルトのまま追加

- "Interface and Protocols" -> "Serial" -> "JTAG UART"を選択、デフォルトのまま追加

- "Processors and Peripherals" -> "Peripherals" -> "PIO (Parallel I/O)"を選択、"Basic Setting"の"Direction:"を"Output"に変更、 他はデフォルトで"Finish"

- clk(赤)、reset(青)、memory(緑)、IRQ(紫)を以下の通りに接続

- PIOの"Conduit"の"Export"をダブルクリックして名前を付ける(オレンジ、デフォルトのままでよい)

- Nios IIのIPを右クリックして"Editを選択

- "Address Map"タグを選択、メニューから"System" -> "Assign Base Addresses"を選択 - 以前のQsysではデフォルトのメモリーアドレスの衝突を自分で解決する必要があったが、このバージョンでは自動化されている

これで、下の"Message"欄のエラーが全部消えたはずだ、下の"Generate HDL"を押して統合IPモジュールを作成する、

"Save changes to unnamed?"のダイアログが出たら、適当な名前(nios2_PIOLED_qsys.qsys)を付け、"保存”する

後は勝手にやってくれるので、終わったらダイアログを"Close"して、Platform Designerを終了する、

(20200120改定)

Quartus Primeに戻り、"Project" -> "Add/Remove Files in Project"を選択し、qsysファイルをプロジェクトに追加する

トップモジュールを追加、FPGAイメージ作成、フラッシュ

- "File" -> "New"で"Verilog HDL file"を選択、以下のようにトップモジュールを記述して保存

module nios2_PIOLED( input wire in_clk, input wire [9:0] in_switch, input wire [3:0] in_button, output wire [9:0] out_led, output wire [6:0] seven_segment_0, output wire [6:0] seven_segment_1, output wire [6:0] seven_segment_2, output wire [6:0] seven_segment_3, output wire [6:0] seven_segment_4, output wire [6:0] seven_segment_5); // // terminate unnecessary LEDs // assign seven_segment_0 = 7'd0; assign seven_segment_1 = 7'd0; assign seven_segment_2 = 7'd0; assign seven_segment_3 = 7'd0; assign seven_segment_4 = 7'd0; assign seven_segment_5 = 7'd0; // assign out_led[9:8] = 2'b0; // nios2_PIOLED_qsys nios2_PIOLED_qsys( .clk_clk(in_clk), // clk.clk .pio_0_external_connection_export(out_led[7:0]), // pio_0_external_connection.export .reset_reset_n(in_button[0]) // reset.reset_n ); endmodule

(20200120改定)

Qsysで作成したトップモジュール(nios2_PIOLED_qsys)のVerilog定義は、プロジェクトフォルダーの下に上で保存した名前(nios2_PIOLED_qsys)のフォルダの中の"synthesis"フォルダの中にある(nios2_PIOLED_qsys.v)。

Nios II上で動作させるプログラムを作成し、実行する

- Quartus Primeに戻り、"Tools" -> "Nios II Software Build Tools for Eclipse"を起動

- "Select a workplace"のダイアログが出るので、現行のプロジェクトフォルダーの下に"software"というフォルダーを作り、それをworkspaceに設定する

- Eclipseで、"File" -> "New" -> "Nios II Application and BSP from Template"を選択

- "SOPC Information File name"のファイル選択ボタン("...")を押し、現行のプロジェクトフォルダーの下にある.sopcinfo(nios2_PIOLED_qsys.sopcinfo)を選択、読み込まれるとデフォルトが設定される

- "Project name"を適当に(nios2_PIOLED_sw)つける

- "Project template"から"Hello World Small"を選択し、"Next"を押す

- 次のページで"Create a new BSP project based on the application project template"にチェックが入っていることを確認、"Finish"を押す

これでsopcinfoを元にBSPファイルが生成され、必要なライブラリーがプロジェクトに取り込まれる。

- "Project Explorer"のプロジェクトフォルダ(nios2_PIOLED_sw)を展開し、"hello_world_small.c"をプロジェクト名(nios2_PIOLED_sw.c)に変更、ファイルを右クリックするとドロップダウンメニューから"Rename..."を選択できる

- 上記のファイルを開く(ダブルクリック)、以下のように変更

#include "system.h"

#include "altera_avalon_pio_regs.h"

int main()

{

IOWR_ALTERA_AVALON_PIO_DATA(PIO_0_BASE,0x01);

/* Event loop never exits. */

while (1);

return 0;

}

- "Project" -> "Build All"を選択

さあ、いよいよリモート実行だ。

- "Run" -> "Debug Configurations"を選択

元に戻すのには"Window" -> "Perspective" -> "Nios" -> "Open Perspective" -> "Nios II"だ。

この状態でメインの一番最初の関数でブレークがかかっているので、

- "Resume"ボタンを押す

LED0 (PIOのbit 0にマップされている)が点灯すれば、成功だ。

"Terminate"ボタンを押せば、デバッグ終了となる。

以上、以前にQurtus II 13.1 & Qsysの組み合わせでNios IIを組み込み、リモートデバッグしたときとほとんど変わりはなかった。

Qsysの名前が"Platform Designer"と変わったこと、IP Catalogのカテゴリーが変わったことの2つが戸惑ったくらいだ。

QuartusのHigh DPIでの表示不具合の対策

さてDE0-CVも入手し、新しいツール群での動作確認を進める筆者。

過去のQuartusでもそうだったが、最近のHigh DPIのPCを使用すると、QuartusやEclipseなどでアイコンがどうしようもなく小さくなったり、ダイアログの各部品が縮んだりしてしまい、まともに操作できなくなってしまうことがある。

#筆者はMSFT Surface Pro 4で使用中。

そんな際のtips。

- regeditで、"HKEY_LOCAL_MACHINE\SOFTWARE\Microsoft\Windows\CurrentVersion\SideBySide"にDWORD値"PreferExternalManifest"を作り、値を"1"にする、再起動

- テキストエディターを開き、以下をコピペ、"temp.manifest"として保存

<?xml version="1.0" encoding="UTF-8" standalone="yes"?>

<assembly xmlns="urn:schemas-microsoft-com:asm.v1" manifestVersion="1.0" xmlns:asmv3="urn:schemas-microsoft-com:asm.v3">

<description>eclipse</description>

<trustInfo xmlns="urn:schemas-microsoft-com:asm.v2">

<security>

<requestedPrivileges>

<requestedExecutionLevel xmlns:ms_asmv3="urn:schemas-microsoft-com:asm.v3"

level="asInvoker"

ms_asmv3:uiAccess="false">

</requestedExecutionLevel>

</requestedPrivileges>

</security>

</trustInfo>

<asmv3:application>

<asmv3:windowsSettings xmlns="http://schemas.microsoft.com/SMI/2005/WindowsSettings">

<ms_windowsSettings:dpiAware xmlns:ms_windowsSettings="http://schemas.microsoft.com/SMI/2005/WindowsSettings">false</ms_windowsSettings:dpiAware>

</asmv3:windowsSettings>

</asmv3:application>

</assembly>

- 上で作ったmanifestファイルを以下のフォルダにrenameして保存

筆者はQuartus Prime 17.1を使用しているが、デフォルトでインストールしていれば(FPGA Tool Home)は"C:\intelFPGA_lite\17.1"のはずだ。

これでQuartusとEclipseの表示不具合は対策できる。

他にも問題になるツールがある場合には、そのツールのフォルダにこのmanifestファイルをコピーして、(ツールのファイル名(含む.exe)).manifestとして保存すれば、High DPIのスケーリングに対応して表示される。

・・・ちょっと大きくなりすぎるんだけど、使えるので良しとしよう。

DE0-CVで(大げさな)Lチカ

動作確認、さぁ行ってみようかぁ。

- Quartus Primeを起動、"File" -> "New Project Wizard"を選択、プロジェクト名は"LEDBlink"、詳細設定はこちらの中で参照しているこちらを参照、"Family & Device Setting"を"5CEBA4F23C7"にするのを忘れずに。

- "File" -> "New..."で"Verilog HDL"を選択、以下の通りに実装、"LEDBlink.v"で保存

module LEDBlink( input wire in_clk, input wire [9:0] in_switch, input wire [3:0] in_button, output wire [9:0] out_led, output wire [6:0] seven_segment_0, output wire [6:0] seven_segment_1, output wire [6:0] seven_segment_2, output wire [6:0] seven_segment_3, output wire [6:0] seven_segment_4, output wire [6:0] seven_segment_5); // wire reset = ~in_button[0]; // // clock divder for 1 sec // reg [25:0] _26bit_counter; wire _26bit_counter_expired; assign _26bit_counter_expired = (_26bit_counter == 26'd49_999_999)? 1'b1: 1'b0; // always @(posedge in_clk or posedge reset) begin if (reset) _26bit_counter <= 26'd0; else begin if (_26bit_counter_expired) _26bit_counter <= 26'd0; else _26bit_counter <= _26bit_counter + 26'd1; end end // // LED blink latch // reg led_latch; // always @(posedge in_clk or posedge reset) begin if (reset) led_latch <= 1'd0; else if (_26bit_counter_expired) led_latch <= ~led_latch; end // // counter for 7 segment LED // reg [3:0] _4bit_counter; // always @(posedge in_clk or posedge reset) begin if (reset) _4bit_counter <= 4'd0; else if (_26bit_counter_expired) _4bit_counter <= _4bit_counter + 4'd1; end //assign LEDs seven_segment_decoder seven_segment_decoder_0( .in_4bit(_4bit_counter + 4'd5), .out_seven_segment(seven_segment_0)); seven_segment_decoder seven_segment_decoder_1( .in_4bit(_4bit_counter + 4'd4), .out_seven_segment(seven_segment_1)); seven_segment_decoder seven_segment_decoder_2( .in_4bit(_4bit_counter + 4'd3), .out_seven_segment(seven_segment_2)); seven_segment_decoder seven_segment_decoder_3( .in_4bit(_4bit_counter + 4'd2), .out_seven_segment(seven_segment_3)); seven_segment_decoder seven_segment_decoder_4( .in_4bit(_4bit_counter + 4'd1), .out_seven_segment(seven_segment_4)); seven_segment_decoder seven_segment_decoder_5( .in_4bit(_4bit_counter), .out_seven_segment(seven_segment_5)); // assign out_led = (led_latch)? 10'b11_1111_1111: 10'b00_0000_0000; endmodule

- "File" -> "New..."で"Verilog HDL"を選択、以下の通りに実装、こちらは"seven_segment_decoder.v"で保存

module seven_segment_decoder( input wire [3:0] in_4bit, output wire [6:0] out_seven_segment); // function [6:0] led_decoder; // input [3:0] in_number; // begin case (in_number) 4'h0: led_decoder = 7'b1000000; 4'h1: led_decoder = 7'b1111001; 4'h2: led_decoder = 7'b0100100; 4'h3: led_decoder = 7'b0110000; 4'h4: led_decoder = 7'b0011001; 4'h5: led_decoder = 7'b0010010; 4'h6: led_decoder = 7'b0000010; 4'h7: led_decoder = 7'b1111000; 4'h8: led_decoder = 7'b0000000; 4'h9: led_decoder = 7'b0011000; 4'ha: led_decoder = 7'b0001000; 4'hb: led_decoder = 7'b0000011; 4'hc: led_decoder = 7'b0100111; 4'hd: led_decoder = 7'b0100001; 4'he: led_decoder = 7'b0000110; 4'hf: led_decoder = 7'b0001110; default: led_decoder = 7'b1111111; endcase end endfunction // assign out_seven_segment[6:0] = led_decoder(in_4bit); // endmodule

- 一度、Quartus Primeを終了、プロジェクトフォルダー下の"(project名).qsf"をテキストエディターで開き、以下をコピペ。

set_location_assignment PIN_M6 -to in_button[3] set_location_assignment PIN_M7 -to in_button[2] set_location_assignment PIN_U7 -to in_button[0] set_location_assignment PIN_W9 -to in_button[1] set_location_assignment PIN_U13 -to in_switch[0] set_location_assignment PIN_V13 -to in_switch[1] set_location_assignment PIN_T13 -to in_switch[2] set_location_assignment PIN_T12 -to in_switch[3] set_location_assignment PIN_AA15 -to in_switch[4] set_location_assignment PIN_AB15 -to in_switch[5] set_location_assignment PIN_AA14 -to in_switch[6] set_location_assignment PIN_AA13 -to in_switch[7] set_location_assignment PIN_AB13 -to in_switch[8] set_location_assignment PIN_AB12 -to in_switch[9] set_location_assignment PIN_AA2 -to out_led[0] set_location_assignment PIN_AA1 -to out_led[1] set_location_assignment PIN_W2 -to out_led[2] set_location_assignment PIN_Y3 -to out_led[3] set_location_assignment PIN_N2 -to out_led[4] set_location_assignment PIN_N1 -to out_led[5] set_location_assignment PIN_U2 -to out_led[6] set_location_assignment PIN_U1 -to out_led[7] set_location_assignment PIN_L2 -to out_led[8] set_location_assignment PIN_L1 -to out_led[9] set_location_assignment PIN_U21 -to seven_segment_0[0] set_location_assignment PIN_V21 -to seven_segment_0[1] set_location_assignment PIN_W22 -to seven_segment_0[2] set_location_assignment PIN_W21 -to seven_segment_0[3] set_location_assignment PIN_Y22 -to seven_segment_0[4] set_location_assignment PIN_Y21 -to seven_segment_0[5] set_location_assignment PIN_AA22 -to seven_segment_0[6] set_location_assignment PIN_AA20 -to seven_segment_1[0] set_location_assignment PIN_AB20 -to seven_segment_1[1] set_location_assignment PIN_AA19 -to seven_segment_1[2] set_location_assignment PIN_AA18 -to seven_segment_1[3] set_location_assignment PIN_AB18 -to seven_segment_1[4] set_location_assignment PIN_AA17 -to seven_segment_1[5] set_location_assignment PIN_U22 -to seven_segment_1[6] set_location_assignment PIN_Y19 -to seven_segment_2[0] set_location_assignment PIN_AB17 -to seven_segment_2[1] set_location_assignment PIN_AA10 -to seven_segment_2[2] set_location_assignment PIN_Y14 -to seven_segment_2[3] set_location_assignment PIN_V14 -to seven_segment_2[4] set_location_assignment PIN_AB22 -to seven_segment_2[5] set_location_assignment PIN_AB21 -to seven_segment_2[6] set_location_assignment PIN_Y16 -to seven_segment_3[0] set_location_assignment PIN_W16 -to seven_segment_3[1] set_location_assignment PIN_Y17 -to seven_segment_3[2] set_location_assignment PIN_V16 -to seven_segment_3[3] set_location_assignment PIN_U17 -to seven_segment_3[4] set_location_assignment PIN_V18 -to seven_segment_3[5] set_location_assignment PIN_V19 -to seven_segment_3[6] set_location_assignment PIN_U20 -to seven_segment_4[0] set_location_assignment PIN_Y20 -to seven_segment_4[1] set_location_assignment PIN_V20 -to seven_segment_4[2] set_location_assignment PIN_U16 -to seven_segment_4[3] set_location_assignment PIN_U15 -to seven_segment_4[4] set_location_assignment PIN_Y15 -to seven_segment_4[5] set_location_assignment PIN_P9 -to seven_segment_4[6] set_location_assignment PIN_N9 -to seven_segment_5[0] set_location_assignment PIN_M8 -to seven_segment_5[1] set_location_assignment PIN_T14 -to seven_segment_5[2] set_location_assignment PIN_P14 -to seven_segment_5[3] set_location_assignment PIN_C1 -to seven_segment_5[4] set_location_assignment PIN_C2 -to seven_segment_5[5] set_location_assignment PIN_W19 -to seven_segment_5[6] set_location_assignment PIN_M9 -to in_clk

これでDE0-CVボード上の部品との接続ができる。

このピンアサインメントはよく使うので、"Assignments" -> "Export Assignments"を選択し、どこかに保存して置くと他のプロジェクトでインポートできる。

DE0-CV導入

遅々としながらも、趣味FPGAプロジェクトは継続している。

FPGA ボードで学ぶ組込みシステム開発入門 ?Altera編?

- 作者: 小林優

- 出版社/メーカー: 技術評論社

- 発売日: 2011/09/22

- メディア: 大型本

- 購入: 3人 クリック: 31回

- この商品を含むブログ (19件) を見る

この本の著者が改訂版である

![【改訂2版】FPGAボードで学ぶ 組込みシステム開発入門[Intel FPGA編] 【改訂2版】FPGAボードで学ぶ 組込みシステム開発入門[Intel FPGA編]](https://images-fe.ssl-images-amazon.com/images/I/618bhgdkfUL._SL160_.jpg)

【改訂2版】FPGAボードで学ぶ 組込みシステム開発入門[Intel FPGA編]

- 作者: 小林優

- 出版社/メーカー: 技術評論社

- 発売日: 2018/01/19

- メディア: 大型本

- この商品を含むブログ (1件) を見る

前半は前の本からツール類を更新した(Quartus Prime、Qsys)程度だが、後半にはSDRAMを利用したVGAコントローラやCMOSカメラコントローラなど、魅かれる内容だ。

動作速度のため、推奨FPGAがCyclone Vに変更になった。

今後Cyclone V SoCに着手しようと考えていたので、ツールを最新のものに更新することも考えてCyclone Vの開発キットであるTerasic DE0-CVを購入した。

新しい開発ツールであるQuartus Primeだが・・・ほとんどQuartus II。

基本的にDE0の開発で使用していたQuartus II 13.1と比較して、Quartus、Qsys、ModelSim Altera、Nios II Software Build Tool for Eclipseといったツールチェーンは変わらない。

変わったのはわずかにIP Catalog(旧Megawizard、Alteraが供給するソフトIP)くらいか。

ツールであるQuartus Primeはこちらからダウンロードできる、無償のLight Editionで十分である。

https://www.altera.co.jp/products/design-software/fpga-design/quartus-prime/download.html

ダウンロードページではオプションが選択できる、Quartus Prime(含むModelSim - Intel FPGA Edition (aka ModelSim - Altera))とCyclone V device supportだけをダウンロードすればよい。

Akamai DL3をインストールしていない場合は、こちらを先にインストールする - あとあと面倒が少なくてすむ。

ダウンロードが完了したら、Quartus Primeのインストーラを起動する、あとは勝手にすべて導入してくれる。

インストールが終わったら、Quartus Primeを起動、さっそく動作確認だ。

プロジェクトの作成方法はQuartus IIと一緒、こちらの通り進めればよい。

唯一違うのはターゲットデバイスの設定で、DE0-CVに搭載されているCyclone Vは"5CEBA4F23C7"だ。

Terasic DE0-CVはほぼDE0コンパチで、DE0で開発したVerilog HDLの資産はかなりが継承できる。

外見上の違いは7セグLEDが4個から6個に、ボタンが3個から4個+デバイスリセットに、SDスロットがマイクロSDスロットになったくらいだ。

スマートウォッチ(Ticwatch E)を購入 - 1年ぶり4回目

わずか2か月でHuawei Watchと別れて、一年が経った。

Huawei Watchに関しては短い付き合いになると覚悟の上であったが、最初のmoto360も、Apple Watchも「コレジャナイ感」は半端なく、どうにも「スマートウォッチ」とは思えなかったのだ。

よっぽどスマート(笑)さのかけらのないGarmin Forerunner 225の方が、筆者には実用的スマートウォッチだ。

昨年の年末商戦前に出たIDCの予想以降も、IT業界ではスマートウォッチのオワコンぶりが変わりなく、いわゆるIT・ガジェット系のニュースで見ることは稀になってきた。

しかしマーケティング的には、ここにきて面白くなってきている。

フォッシルや、タグホイヤー、モンブランなどの腕時計デザインブランドがコンスタントに新製品を出してきているのだ。

カシオも昨年Protekのラインにスマートウォッチを追加した。

しかも、タグホイヤーやモンブランなどの「高級」ブランドやカシオのものを除くと、市場価格がほぼ$200前後で横並びだ、安くはない。

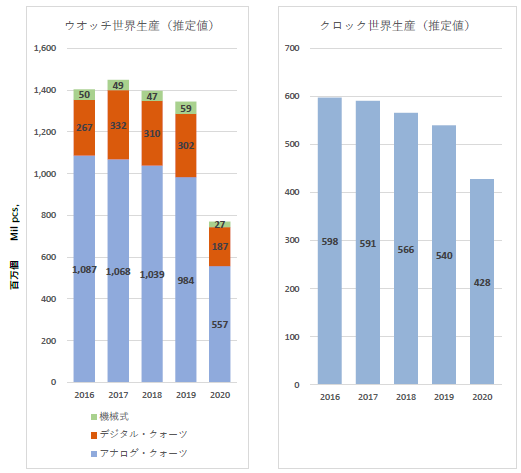

腕時計市場とはどんな市場なのだろうか。

この業界の方は大変親切で、こんな貴重な資料をネットでロハで公開してくれている。

- 全世界の腕時計の生産台数は年間14億台で、年間成長率がほぼ0

- そのうち95%以上がクォーツ、つまりホームセンターなどでキュッパやイチキュッパで売っているあれ

こんな市場で在庫が山のように膨れ上がることは考えられないので、生産台数=出荷台数だろう、FIFOだ。

スマートウォッチの出荷台数が年間おおよそ2000万台、全世界腕時計の1%強となる。

よくいう「アーリーアダプター」というのは市場の+σテール、つまり16%。

つまりスマートウォッチを腕時計市場全体でみると、アーリーアダプターさえつかみ損ね、見事にChasmの谷に落ちたことになるのだ。

ちなみにスマホ(笑)の年間生産台数は20億台に届くほどで、台数規模としては腕時計に並ぶ。

IT業界からすれば、2匹目の>10億台市場への挑戦は見事に失敗に終わったわけだ。

ところが、これを腕時計市場のプレーヤーから見たらどうだろうか?

こちらとこちらに腕時計市場の変遷を書かれている方がいるのだが、他の市場と同様に技術の水準化によるコモディティー化が一気に進んだ後に、「良質で安く手に入る大量生産品」と「差別化のすすんだ寡少な高級品」との市場のセグメント化が進んだのだ。

他の市場って何?という方は、車を見よう、PCを見よう。

どちらも年間出荷台数がおおよそ1億台の市場だが、見事なセグメント化が進んでいる。

腕時計のセグメントの規模に関する情報がないのだが、一般的なセオリー通りであれば+σテール、つまり16%がこの「差別化による高級品」の市場規模だろう。

だとすれば、スマートウォッチの1%強の腕時計市場への上積みは、差別化腕時計を作っている腕時計デザインブランドからすれば10%近い市場拡大に見えるはずだ。

新しいセグメント、売り上げ台数10%上積み、そりゃ、やるだろう、やるしかないだろう。

スマートウォッチのラインナップ化をやるだろう。

返ってこの市場の顧客からみたらどうだろうか?

このご時世に腕時計を買ってつける御仁は、価格はどうであれ与太郎だ。

スマートかそうでないかはともかく、気に入れば買うだろう。

自分の好きな腕時計デザインブランドが新作を出したら、たとえ10本目だろうが20本目だろうが買うだろう、与太郎だ。

そしてスマートかそうでないかは、気にとめないだろう。

ここが筆者も大きくつまづいていたところだ。

「スマートウォッチ」という言葉にとらわれすぎていて、何か特別な腕時計にできない「機能」を求めていたのだ。

そんなものは「垂直差別化」の終わった腕時計市場では、日本の時計メーカーがしのぎを削る「ソーラー腕時計」「電波腕時計」「GPS腕時計」と変わらないのだ。

なにもなくたって、ブランドインテマシーとフェイスリフトで物は売れるのだ。

ただ、その市場規模はIT業界のお気に召すものではなかっただけなのだ。

ちなみに筆者は高機能腕時計マンセーで、キナティックもソーラー式三波電波腕時計も所有している、別な意味で与太郎だ。

GPS腕時計ももう少し値ごろになったらぜひ購入したいと考えている。

全てクロノグラフ付だ。

こんな筆者ならスマートでないスマートウォッチを一本ぐらい持っていてもよいだろう。

ということで、4度目のお迎えをすることにした。

Ticwatch E超軽量スマートウォッチShadow アンドロイド・ウエア2.0搭?iOSおよびアンドロイド

- 出版社/メーカー: Mobvoi

- メディア: Wireless Phone Accessory

- この商品を含むブログを見る

![[カシオ]CASIO スマートアウトドアウォッチ プロトレックスマート GPS搭載 WSD-F20-RG メンズ [カシオ]CASIO スマートアウトドアウォッチ プロトレックスマート GPS搭載 WSD-F20-RG メンズ](https://images-fe.ssl-images-amazon.com/images/I/51YteS1Ap1L._SL160_.jpg)

[カシオ]CASIO スマートアウトドアウォッチ プロトレックスマート GPS搭載 WSD-F20-RG メンズ

- 出版社/メーカー: CASIO(カシオ)

- 発売日: 2017/04/21

- メディア: 時計

- この商品を含むブログ (1件) を見る

キャズム Ver.2 増補改訂版 新商品をブレイクさせる「超」マーケティング理論

- 作者: ジェフリー・ムーア,川又政治

- 出版社/メーカー: 翔泳社

- 発売日: 2014/10/04

- メディア: 単行本(ソフトカバー)

- この商品を含むブログ (2件) を見る

GPD Pocketがスリープさせて蓋を閉じると勝手に復帰してしまい、がんがんバッテリーを食ってお困りの貴兄に(解決編)

さて今まで、

- スリープさせたGPD Pocketが勝手に復帰してディスプレイが点灯し、がんがんバッテリーを食ってお困りの貴兄に - 米国で働く技術系サラリーマンのボヤキ on はてブロ

- GPD Pocketのホールセンサーの誤作動で、スリープさせたのに蓋を閉じると勝手に復帰してしまい、がんがんバッテリーを食ってお困りの貴兄に - 米国で働く技術系サラリーマンのボヤキ on はてブロ

- GPD Pocketのホールセンサーをぬっころしたのに、スリープさせて蓋を閉じると勝手に復帰してしまい、がんがんバッテリーを食ってお困りの貴兄に - 米国で働く技術系サラリーマンのボヤキ on はてブロ

- GPD Pocketのホールセンサーをぬっころしてカバーを開いたときのアクションも無効にしたのに、スリープさせて蓋を閉じると勝手に復帰してしまい、がんがんバッテリーを食ってお困りの貴兄に - 米国で働く技術系サラリーマンのボヤキ on はてブロ

と4度に渡って対策してきた、通称「スリープ死」問題。

しかし、それでも治らなかった筆者のGPD Pocket。

こいつは2台目で、一台目ではこんな不具合はなかったのに、なぜ?と思い、ハタと気が付いた。

nobu-macsuzuki.hatenablog.com

これ。

これのおかげで、キーボードやクリクリトラックパッドがディスプレイ側に当たり、USB HIDメッセージでGPD Pocketを起こしてしまうのを防いでいたのだ。

さっそく再度クッションをつけたところ、ぴたりとおさまった。

後で、上の変更も一つづつ戻してみよう。