さらに新しいツールに慣れるため、IP統合の復習としてNios IIを組み込んだ簡単なモジュールを作る。

やっていることは

Qsysを使ってNios IIを組み込んだモジュールを作成する - 米国で働く技術系サラリーマンのボヤキ on はてブロ

と、

Quartus IIでQsysで作成したモジュールを組み込む - 米国で働く技術系サラリーマンのボヤキ on はてブロ

とほぼ同じことだ。

Quartus Primeでプロジェクトを作成

Platform Designer(旧Qsys)でNios IIを組み込んだモジュールを作成する

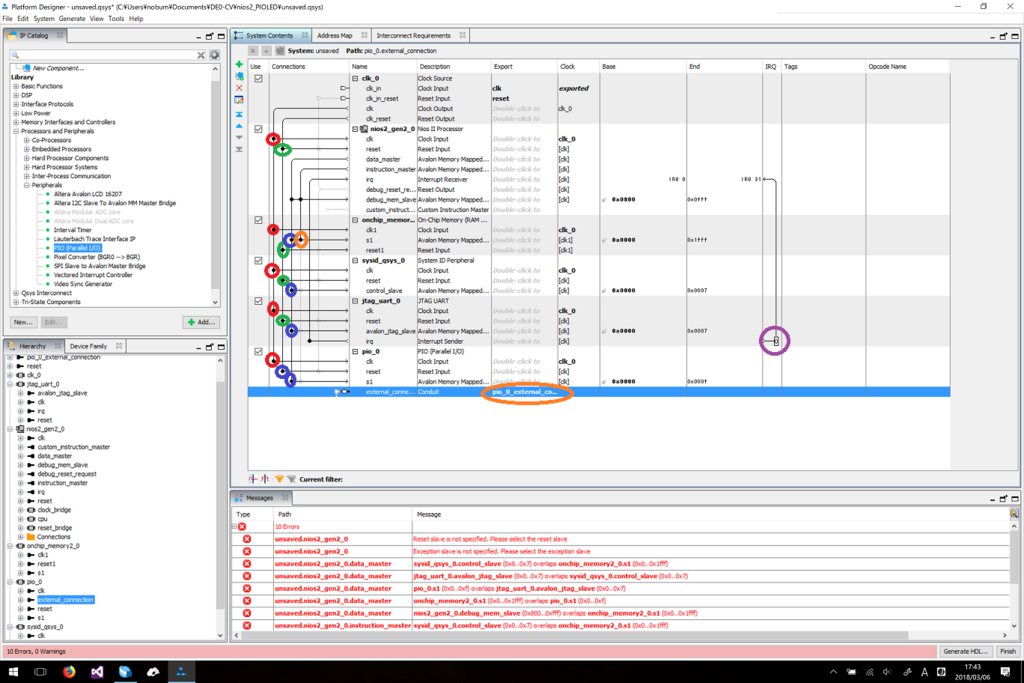

- "Tool" -> "Platform Designer"を起動、"IP Catalog"から以下のIPを組み込んでいく

- "Processors and Peripherals" -> "Embedded Processor" -> "Nios II Processor"を選択、"Main"タグで"Nios II Core"は"Nios II/e"を選択、他はデフォルトで"Finish"

- "Basic Function" -> "On Chip Memory" -> "On-Chip Memory (RAM or ROM)"を選択、"Size" -> "Total Memory Size"を"8192(bytes)"に変更、他はデフォルトで"Finish"

- "Basic Function" -> "Simulation: Debug and Verification" -> "Debug and Performance" -> "System ID Peripheral"を選択、デフォルトのまま追加

- "Interface and Protocols" -> "Serial" -> "JTAG UART"を選択、デフォルトのまま追加

- "Processors and Peripherals" -> "Peripherals" -> "PIO (Parallel I/O)"を選択、"Basic Setting"の"Direction:"を"Output"に変更、 他はデフォルトで"Finish"

- clk(赤)、reset(青)、memory(緑)、IRQ(紫)を以下の通りに接続

- PIOの"Conduit"の"Export"をダブルクリックして名前を付ける(オレンジ、デフォルトのままでよい)

- Nios IIのIPを右クリックして"Editを選択

- "Address Map"タグを選択、メニューから"System" -> "Assign Base Addresses"を選択 - 以前のQsysではデフォルトのメモリーアドレスの衝突を自分で解決する必要があったが、このバージョンでは自動化されている

これで、下の"Message"欄のエラーが全部消えたはずだ、下の"Generate HDL"を押して統合IPモジュールを作成する、

"Save changes to unnamed?"のダイアログが出たら、適当な名前(nios2_PIOLED_qsys.qsys)を付け、"保存”する

後は勝手にやってくれるので、終わったらダイアログを"Close"して、Platform Designerを終了する、

(20200120改定)

Quartus Primeに戻り、"Project" -> "Add/Remove Files in Project"を選択し、qsysファイルをプロジェクトに追加する

トップモジュールを追加、FPGAイメージ作成、フラッシュ

- "File" -> "New"で"Verilog HDL file"を選択、以下のようにトップモジュールを記述して保存

module nios2_PIOLED( input wire in_clk, input wire [9:0] in_switch, input wire [3:0] in_button, output wire [9:0] out_led, output wire [6:0] seven_segment_0, output wire [6:0] seven_segment_1, output wire [6:0] seven_segment_2, output wire [6:0] seven_segment_3, output wire [6:0] seven_segment_4, output wire [6:0] seven_segment_5); // // terminate unnecessary LEDs // assign seven_segment_0 = 7'd0; assign seven_segment_1 = 7'd0; assign seven_segment_2 = 7'd0; assign seven_segment_3 = 7'd0; assign seven_segment_4 = 7'd0; assign seven_segment_5 = 7'd0; // assign out_led[9:8] = 2'b0; // nios2_PIOLED_qsys nios2_PIOLED_qsys( .clk_clk(in_clk), // clk.clk .pio_0_external_connection_export(out_led[7:0]), // pio_0_external_connection.export .reset_reset_n(in_button[0]) // reset.reset_n ); endmodule

(20200120改定)

Qsysで作成したトップモジュール(nios2_PIOLED_qsys)のVerilog定義は、プロジェクトフォルダーの下に上で保存した名前(nios2_PIOLED_qsys)のフォルダの中の"synthesis"フォルダの中にある(nios2_PIOLED_qsys.v)。

Nios II上で動作させるプログラムを作成し、実行する

- Quartus Primeに戻り、"Tools" -> "Nios II Software Build Tools for Eclipse"を起動

- "Select a workplace"のダイアログが出るので、現行のプロジェクトフォルダーの下に"software"というフォルダーを作り、それをworkspaceに設定する

- Eclipseで、"File" -> "New" -> "Nios II Application and BSP from Template"を選択

- "SOPC Information File name"のファイル選択ボタン("...")を押し、現行のプロジェクトフォルダーの下にある.sopcinfo(nios2_PIOLED_qsys.sopcinfo)を選択、読み込まれるとデフォルトが設定される

- "Project name"を適当に(nios2_PIOLED_sw)つける

- "Project template"から"Hello World Small"を選択し、"Next"を押す

- 次のページで"Create a new BSP project based on the application project template"にチェックが入っていることを確認、"Finish"を押す

これでsopcinfoを元にBSPファイルが生成され、必要なライブラリーがプロジェクトに取り込まれる。

- "Project Explorer"のプロジェクトフォルダ(nios2_PIOLED_sw)を展開し、"hello_world_small.c"をプロジェクト名(nios2_PIOLED_sw.c)に変更、ファイルを右クリックするとドロップダウンメニューから"Rename..."を選択できる

- 上記のファイルを開く(ダブルクリック)、以下のように変更

#include "system.h"

#include "altera_avalon_pio_regs.h"

int main()

{

IOWR_ALTERA_AVALON_PIO_DATA(PIO_0_BASE,0x01);

/* Event loop never exits. */

while (1);

return 0;

}

- "Project" -> "Build All"を選択

さあ、いよいよリモート実行だ。

- "Run" -> "Debug Configurations"を選択

元に戻すのには"Window" -> "Perspective" -> "Nios" -> "Open Perspective" -> "Nios II"だ。

この状態でメインの一番最初の関数でブレークがかかっているので、

- "Resume"ボタンを押す

LED0 (PIOのbit 0にマップされている)が点灯すれば、成功だ。

"Terminate"ボタンを押せば、デバッグ終了となる。

以上、以前にQurtus II 13.1 & Qsysの組み合わせでNios IIを組み込み、リモートデバッグしたときとほとんど変わりはなかった。

Qsysの名前が"Platform Designer"と変わったこと、IP Catalogのカテゴリーが変わったことの2つが戸惑ったくらいだ。