さて、あまり弊ブログではあまり人気のない、しかし筆者が今ご執心なVerilogのことも書いておこう。

FPGA ボードで学ぶ組込みシステム開発入門 ?Altera編?

- 作者: 小林優

- 出版社/メーカー: 技術評論社

- 発売日: 2011/09/22

- メディア: 大型本

- 購入: 3人 クリック: 31回

- この商品を含むブログ (19件) を見る

組み込みRAMへの書き込みも立ち上がりでできるかのように書いている、上記の本でもコメントで書かれている。

RAMの世界では当たり前なのだが、果たして本当だろうか?

検証してみる。

今回は、ラッパーの回路を書かず、テストベンチで直接組み込みRAMを制御する。

こちらと同じ8bits/word x 16wordsの2-portのRAMを作って、以下のようなベンチを実行する。

in_clk <= 1'b0; in_data <= 8'haa; in_read_address <= 4'b0000; in_write_address <= 4'b0000; in_write_enable <= 1'b1; #5 in_clk <= 1'b1; #5 in_data <= 8'h55; #5 in_clk <= 1'b0; #5 in_write_enable <= 1'b0; #5 in_clk <= 1'b1; #5 in_clk <= 1'b0; #5 in_clk <= 1'b1; #5

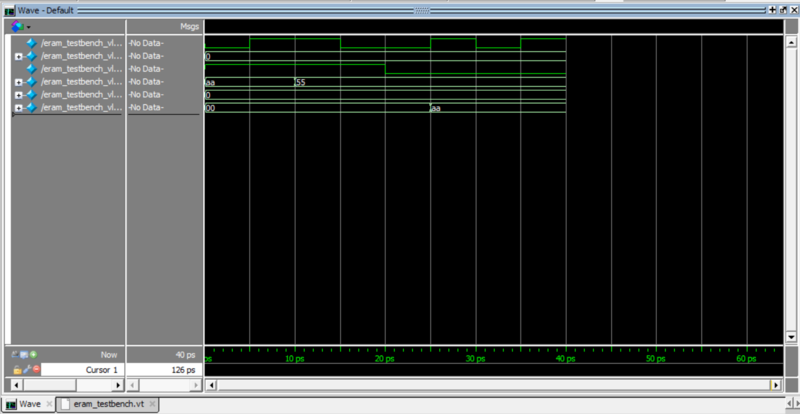

結果はこんな感じだ。

果たして、アドレス0x0にクロック立ち上がり時にデータバスに0xaaを、立ち下り時に0x55をセットすると、次の立ち上がりで同じアドレスから0xaaが読み出される。

つまり、立ち上がりで書き込んでいるのだ。